preface

VHDL- Very-High-Speed Integrated Circuit Hardware Description Language

CPLD- Complex Programmable Logic Device

FPGA- Field-Programmable Gate Array,现场可编程逻辑门阵列

EDA- Electronic design automation

一、基础

1.0 设计实体

一个VHDL程序对应着一项具体工程设计,通常被称为设计实体。

- 设计实体

- 库

- 程序包

- 实体

- 类属参数说明

- 端口说明

- 结构体

- 结构体说明

- 结构体功能描述

- 配置

1.1 实体

实体用于描述设计实体与外部的接口信号,是设计实体对外的一个通信界面。

ENTITY 实体名 IS

[GENERIC(类属表);] --类属参数说明

[PORT(端口表);] --端口说明

END ENTITY 实体名;

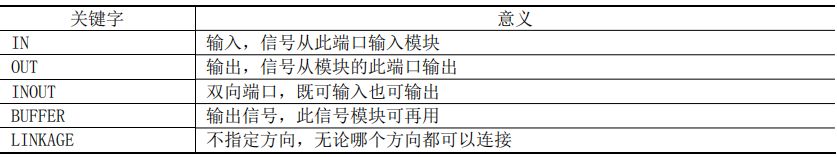

- 端口模式

1.2 结构体

结构体用于描述设计实体的内部结构,是对实体功能的具体实现。

5种功能描述语句之间是 并行 的

ARCHITECTURE 结构体名 OF 实体名 IS

[说明语句]

BEGIN

[功能描述语句]

END ARCHITECTURE 结构体名;

1.3 库

一种用来存储预先完成的程序包和数据集合体的仓库。

LIBRARY 库名

常见的库:IEEE, STD, WORK, VITAL

1.4 程序包

程序包是构成包的单元。

PACKAGE 程序包名 IS

[程序包首说明部分]

END 程序包名;

PACKAGE BODY 程序包名 IS

[程序包体说明部分]

END 程序包名;

1.5 配置

配置用于描述层与层之间的连接关系或实体与结构体之间的连接关系。

CONFIGURATION 配置名 OF 实体名 IS

[配置说明语句]

END 配置名;

1.6 文字规则

- 数字型文字

- 整数文字

- 12_118_008( = 12118008 ), 下划线仅提高可读性

- 实数文字

- 以数制基数表示的文字

- 10#36#2,表示 10 进制数 3600

- 整数文字

- 字符串型文字

- 字符

- 放在

''中的ASCII字符

- 放在

- 字符串

- 放在

""中的一维字符数组

- 放在

- 标识符

- 以英文字母开头

- 不连续使用

_,不以_结尾 - 由英文字母,数字,

_构成 - 不区分大小写

- 字符

- 下标名及下标段名

1.7 数据对象

(1)常量

CONSTANT 常量名:数据类型[:=表达式];

(2)变量

VARIABLE 变量名:数据类型[:=初始值];

(3)信号

在进程和子程序中不允许定义信号,用在顺序语句中。

SIGNAL 信号名:数据类型[:=初始值];

信号赋值目标<=赋值源; --信号的赋值

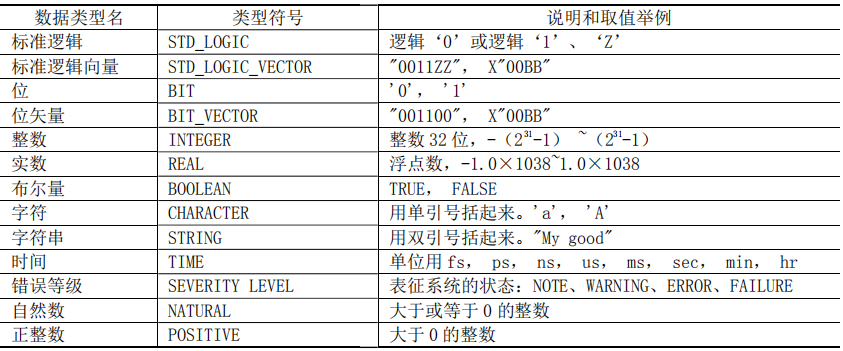

1.8 数据类型

数据类型:标量型,复合类型、指针类型、文件类型

1.9 操作符

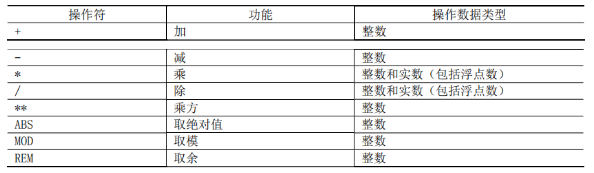

操作符:算术操作符、关系操作符(/=…)、逻辑操作符、符号操作符(+ -)

(一)算术操作符

(三)逻辑操作符

1.10 语句

- 顺序语句

- 赋值语句,

:=<= - 转向控制语句,

IFCASELOOPNEXTEXIT - 等待语句

- 返回语句

RETURN; - 空操作语句

NULL;

- 赋值语句,

- 并行语句

- 进程语句

process- 多个

process之间是并行的

- 多个

- 块语句

block- 块内语句也是并行的

- 并行赋值语句

- 并行过程调用语句

- 元件例化语句

- 进程语句

IF ... THEN

...;

ELSIF ... THEN

...;

ELSIF

...;

END IF;

二、实例

2.1 二输入与非门

LIBRARY IEEE; --申明库

USE IEEE.STD_LOGIC_1164.ALL; --使用库中的包

ENTITY nandgate2 IS --定义一个用于通信的实体

PORT(a,b: IN STD_LOGIC;

y: OUT STD_LOGIC);

END nandgate2;

ARCHITECTURE nand2 OF nandgate2 IS --结构体,实现功能

BEGIN

y <= a NAND b;

END nand2;

2.2 四位加法器

2.3 触发器

参考资料:

- 《数字逻辑》,欧阳星明

- VHDL语法学习笔记