一、计算机系统概述

体系结构:如何设计硬件与软件之间的接口,如指令系统、数据类型、寻址技术、I/O原理。

组成原理:实现计算机体系结构所体现的属性,如具体指令的实现。

1.1 计算机硬件的基本组成

1. 早期的冯诺依曼结构

- 由五大部件组成

- 输入设备

- 输出设备

- 存储器,存放数据和程序

- 运算器,算术运算和逻辑运算

- 控制器,指挥程序运行

- 指令和数据以同等地位存于存储器,可按址寻访

- 指令和数据用二进制表示

- 指令由操作码和地址码组成

- 以运算器为中心

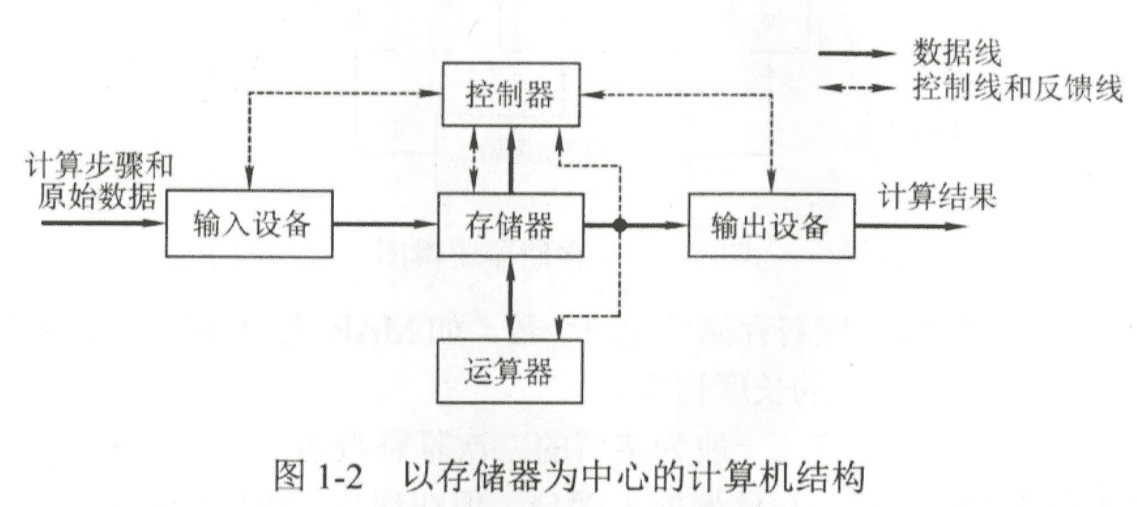

2. 现代计算机的结构

- 以 存储器 为中心

- CPU = 运算器 + 控制器

1.2 计算机系统组成

1. 软件系统

- 系统软件

- 用来管理整个计算机系统

- 应用软件

- 按任务需要编制成的各种程序

2. 硬件系统

| 发展阶段 | 时间 | 逻辑元件 | 速度(次/秒) |

|---|---|---|---|

| 第一代 | 1946~1957 | 电子管 | 几千~几万 |

| 第二代 | 1958~1964 | 晶体管 | 几万~几十万 |

| 第三代 | 1964~1971 | 中小规模集成电路 | 几十万~几百万 |

| 第四代 | 1972~至今 | 大规模、超大规模集成电路 | 上千万~万亿 |

计算机硬件系统是由:I/O设备,运算器,存储器组成的;

它们是通过总线(数据总线,地址总线,控制总线)连接在一起的

- 主存储器

- 存储体

- MAR,存储地址寄存器,MAR位数反映存储单元的个数

- MDR,存储数据寄存器,MDR位数 = 存储字长

- 运算器

- ACC,累加器,用于存放操作数,或运算结果

- MQ,乘商寄存器

- X,通用的操作数寄存器

ALU,算术逻辑单元

- 控制器

- PC,程序计数器,存放下一条指令地址,自动加一

- IR,指令寄存器,存放当前执行的指令

CU,控制单元,分析指令,给出控制信号

1.3 计算机性能指标

1. 存储器的性能指标

总容量 = 存储单元个数 × 存储字长 bit

Eg. MAR 为 32 位, MDR 为 8 位。

总容量 = 2^32 × 8 bit = 4 GB

2. CPU 的性能指标

主频:CPU 内数字脉冲信号的频率。(单位:Hz)

CPI:执行一条指令所需的时钟周期数。

执行一条指令的耗时:CPI × CPU时钟周期

CPU 执行时间:CPU时钟周期数/主频

IPS:每秒执行的指令数 = 主频/平均CPI

FLOPS:每秒执行多少次浮点运算

3. 系统整体的性能指标

数据通路带宽:数据总线一次能并行传送信息的位数

吞吐量:指系统在单位时间内处理请求的数量。

二、数字电路基础与常用器件

2.1 数字电路的基本元件

二极管、双极型三极管(晶体管)、金属-场效应-半导体场效应三极管(MOS管)

2.2 数字电路基础

与或非门

加法器

译码器

数据选择器

触发器

寄存器

2.3 组合逻辑电路与时序逻辑电路

2.4 现场可编程逻辑器件

CPLD、FPGA

三、数据的表示、运算与校验

3.1 表示

- 进位计数制

- 二进制B、八进制O、十进制D、十六进制H

- 进制转化

- 机器数:把正负号数字化的数(存到机器里的样子)

- BCD 码(用二进制编码十进制)

- 8421码

- 余3码

- 2421码

- 通用字符的表示

- ASCII码

- 共 128 个字符

- 0~31、127为控制/通信字符;

- 32~126为可印刷字符

- ASCII码

- 汉字的表示和编码

- 区位码:对应 94×94 二维数组

- 国标码 = 区位码 + 2020H

- 机内码 = 国标码 + 8080H

3.2 运算

二进制加减乘除

- 定点数(小数点的位置固定,Eg.常规计数)

- 无符号数

- 有符号数

- 浮点数(小数点的位置不固定,Eg. 科学计数法)

3.3 校验

由若干位代码组成的一个字叫 码字

将两个码字逐位进行对比,具有不同的位的个数称为 两个码字间的距离

一种编码方案可能有若干个合法码字,两个合法码字间的最小距离称为 码距

设码距为 d, 当 d=1 时,无检错能力;当 d=2 时, 有检错能力;当 d≥3时, 若设计合理,可能具有检错、纠错能力。

- 奇偶校验码(添加一位奇偶校验位)

- 奇校验码:整个校验码(有效信息位和校验位)中 1 的个数为奇数

- 偶校验码:整个校验码(有效信息位和校验位)中 1 的个数为偶数

- 海明校验码

- 设计思路:将信息位分组进行偶校验 -> 多个校验位 -> 多个校验位标注出错位置

- 信息位 n 位,校验位 k 位,需满足:$$2^k \ge n+k+1$$

- 校验位 $P_i$ 放在海明位号为 $2^{i-1}$ 的位置上

- 循环冗余校验码

四、运算器

五、指令系统

六、存储系统

实验

1. TEC-XP+ 教学计算机汇编程序设计

TEC-XP+ 一个双 CPU 的教学计算机系统

- 左 CPU

- 中小规模集成电路实现

- 支持字长:8 位和 16 位

- 右 CPU

- 由 FPGA 芯片实现

| 监控程序指令 | 说明 |

|---|---|

| A[adr] | 汇编写入 |

| U[adr] | 反汇编输出 |

| G[adr] | 运行 |

| p[adr]/T[adr] | 单步执行 |

寄存器说明

- 16个通用寄存器

- R4,16位的堆栈指针 SP

- R5,16位的程序计数器 PC

- IN OUT 的指定寄存器为 R1

实验:借助辅助程序,根据教学机的指令格式,汇编完成程序练习

2. 运算器部件实验

运算器,是 CPU 的重要组成部分,

- Am2901 芯片(4位的运算器)

- ALU

- 通用寄存器(4位,16个)

- Q 寄存器(4位)

- 多路选通器(5组)

3. 组合逻辑控制器实验

#控制器部件的作用:

依据指令内容和指令的执行步骤等,

向计算机的各个部件提供它们每一个步骤协同运行所需要的控制信号。

other

参考资料:

- 计算机组成与体系结构,第三版,宋佳兴

- 王道考研-计算机组成原理

- 学校课程

相关文章: